Udumalai Road, Pollachi, Coimbatore District - 642003

Established in 1998 + Approved by AICTE + Affiliated to Anna University

(A DIVISION OF NIA EDUCATIONAL INSTITUTIONS)

NAAC A++ GRADE Cycle 3 (2023-2030) The Highest Grade

### **Curriculum and Syllabi**

**Semesters I to VI**

**Regulations 2023**

(2023 Batch Only)

Dr. Mahalingam College of Engineering and Technology, Pollachi 642003. (An autonomous institution approved by AICTE and affiliated to Anna University)

#### **Department of B.E. Electronics Engineering (VLSI Design and Technology)**

#### Vision

To strive for excellence in Electronics and Semiconductor Engineering education, research and technological services imparting quality training to students, to make them competent and motivated engineers.

#### Mission:

In order to foster growth and empowerment, we commit ourselves to

- Impart high quality technical education in Electronics and Semiconductor Engineering through effective teaching- learning process and updated curriculum.

- Equip the students with professionalism and technical expertise to provide appropriate solutions to societal and industrial needs.

- Provide stimulating environment with updated facilities to pursue research through creative thinking and team work.

Dr. Mahalingam College of Engineering and Technology, Pollachi 642003. (An autonomous institution approved by AICTE and affiliated to Anna University)

#### **Programme Educational Objectives (PEOs)**

B.E. Electronics Engineering (VLSI Design and Technology) graduates will:

**PEO1.Technical Expertise:** Acquire a professional career and personal development in industries / higher studies / research assignments / entrepreneurs.

**PEO2.Life-long learning:** Sustain to develop their knowledge and skills throughout their career.

**PEO3. Ethical Knowledge:** Exhibit professionalism, ethical attitude, communication skills, team work and adapt to Current trends.

#### **Programme Outcomes (POs) - Regulations 2023**

On successful completion of B.E. Electronics Engineering (VLSI Design and Technology) programme, graduating students/graduates will be able to:

**PO1. Engineering Knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems

**PO2. Problem Analysis:** Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

**PO3. Design/Development of Solutions:** Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

**PO4.** Conduct Investigations of Complex Problems: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions for complex problems.

**PO5. Modern Tool Usage:** Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modelling to complex engineering activities with an understanding of the limitations.

- **PO6.** The Engineer and Society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- **PO7.** Environment and Sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- **PO8. Ethics:** Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- **PO9. Individual and Team Work:** Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- **PO10.** Communication: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- **PO11. Project Management and Finance:** Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments

- **PO12. Life-long learning:** Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

#### **Programme Specific Outcomes (PSOs)**

On successful completion of B.E. Electronics Engineering (VLSI Design and Technology) programme, graduating students/graduates will be able to:

- **PSO1. Design and Implementation of VLSI Circuits:** Design and implement VLSI circuits utilizing appropriate design methodologies and optimization techniques.

- **PSO2.** IC **Design:** Design ICs with optimal performance, power consumption, and area utilization, considering factors such as noise, timing constraints, and signal integrity.

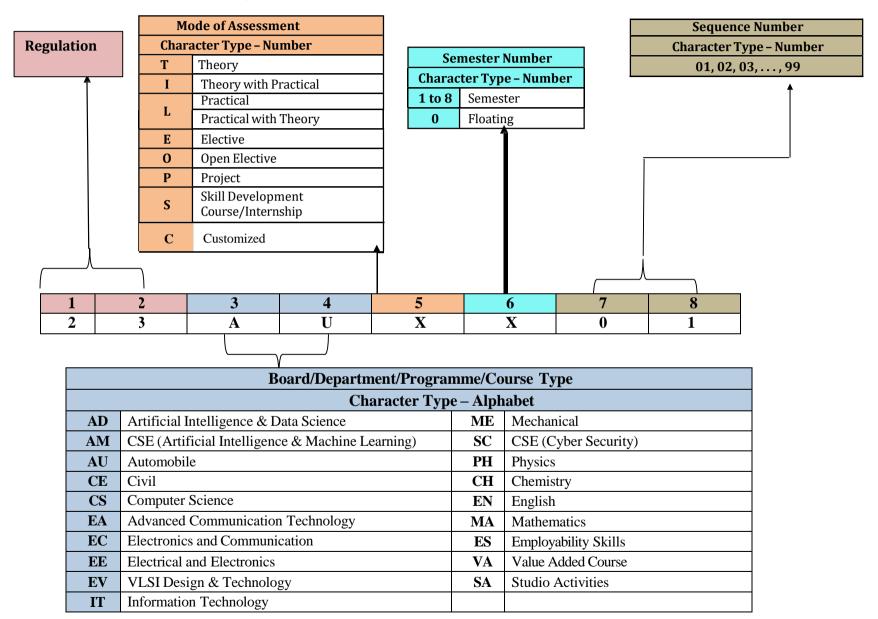

#### Dr. Mahalingam College of Engineering and Technology, Pollachi 2023 Regulation - Course Code Generation Procedure for UG Courses

# Dr. MAHALINGAM COLLEGE OF ENGINEERING AND TECHNOLOGY

The Highest Grade

Udumalai Road, Pollachi, Coimbatore District - 642003

stablished in 1998 • Approved by AICTE • Affiliated to Anna University

# Programme: B.E. Electronics Engineering (VLSI Design and Technology) 2023 Regulations (For 2023 Batch Only) Curriculum for Semester I to VI

| Course<br>Category | Course Code | Course Title      | Duration | Credits | Marks |

|--------------------|-------------|-------------------|----------|---------|-------|

| VAC                | 23VAL101    | Induction Program | 3 Weeks  | -       | 100   |

#### Semester I

| Course                 | Course   | Course Title                        | Ho | urs/W | eek | Credits | Marka | Common to             |

|------------------------|----------|-------------------------------------|----|-------|-----|---------|-------|-----------------------|

| Category               | Code     | Course Title                        | L  | Т     | Р   | Credits | warks | Programmes            |

| AEC                    | 23ENI101 | Communication Skills I              | 2  | 0     | 2   | 3       | 100   | All                   |

| Minor                  | 23MAI102 | Matrices and Calculus               | 3  | 0     | 2   | 4       | 100   | AU,EA,EC,<br>EE,EV&ME |

| Minor                  | 23CHI101 | Chemistry for Electrical Sciences   | 3  | 0     | 2   | 4       | 100   | EC,EE&EV              |

| Major                  | 23ECT101 | Electron Devices                    | 3  | 0     | 0   | 3       | 100   | EA,EC&EV              |

| Multi-<br>Disciplinary | 23ADT001 | C Programming                       | 3  | 0     | 0   | 3       | 100   | CE, EA, EC,& EV       |

| Multi-<br>Disciplinary | 23ADL001 | C Programming Laboratory            | 0  | 0     | 3   | 1.5     | 100   | CE, EA, EC,& EV       |

| VAC                    | 23VAL102 | Wellness for Students               | 0  | 0     | 2   | 1       | 100   | All                   |

| VAC                    | 23VAT101 | தமிழர் மரபு / Heritage of<br>Tamils | 1  | 0     | 0   | 1       | 100   | All                   |

| AEC                    | 23SAL101 | Studio Activities                   | 0  | 0     | 2   | -       | -     | All                   |

|                        |          | Total                               | 15 | 0     | 13  | 20.5    | 800   | -                     |

#### Semester II

| Course                 | Course                  | Course Title                                                         | Ηοι | ırs/ W | /eek | Credits | Marka    | Common to                                   |

|------------------------|-------------------------|----------------------------------------------------------------------|-----|--------|------|---------|----------|---------------------------------------------|

| Category               | Code                    | Course Title                                                         | L   | Т      | Р    | Credits | IVIAI KS | Programmes                                  |

|                        | 23ENI201/               | Communication Skills II                                              | 2   | 0      | 2    |         |          |                                             |

| AEC                    | 23FLT201/               | Foreign Language-Japanese                                            | 3   | 0      | 0    | 3       | 100      | All                                         |

|                        | 23FLT202                | Foreign Language-German                                              | 3   | 0      | 0    | 3       | 100      | All                                         |

| Minor                  | 23MAI202                | Complex Variables and Transforms                                     | 3   | 0      | 2    | 4       | 100      | AU, EC, EE, EV & ME                         |

| Minor                  | 23PHI201                | Physics for Electrical Sciences                                      | 3   | 0      | 2    | 4       | 100      | EA, EC, EE & EV                             |

| Major                  | 23ECT001                | Circuit Theory                                                       | 3   | 0      | 0    | 3       | 100      | EA, EC & EV                                 |

| Multi-<br>Disciplinary | 23ITT202                | Problem Solving and Python Programming                               | 3   | 0      | 0    | 3       | 100      | EA, EC & EV                                 |

| Multi-<br>Disciplinary | 23MEL001                | Engineering Drawing                                                  | 1   | 0      | 3    | 2.5     | 100      | AD,AM,AU,<br>CS,EA,EC, EE,EV,IT,<br>ME & SC |

| Major                  | 23ECL001                | Electric Circuits and Electron Devices Laboratory                    | 0   | 0      | 3    | 1.5     | 100      | EA, EC&EV                                   |

| SEC                    | 23ESL201                | Professional Skills 1: Problem solving skills and Logical Thinking 1 | 0   | 0      | 2    | 1       | 100      | All                                         |

| VAC                    | 23VAT201                | தமிழரும் தொழில் நுட்பமும்/<br>Tamils and Technology                  | 1   | 0      | 0    | 1       | 100      | All                                         |

| Multi-<br>Disciplinary | 23CHT202                | Environmental Sciences                                               | 1   | 0      | 0    | -       | 100      | All                                         |

| AEC                    | 23SAL201                | Studio Activities                                                    | 0   | 0      | 2    | -       | -        | All                                         |

|                        | Total 17 0 16 23 1000 - |                                                                      |     |        |      |         |          |                                             |

#### **Semester III**

| Course                | Course Code | Course Title                                                       | Ηοι | ırs/W | eek | Credits | Marks    | Common to         |

|-----------------------|-------------|--------------------------------------------------------------------|-----|-------|-----|---------|----------|-------------------|

| Category              | Course Code | Course Title                                                       | ┙   | T     | Р   | Credits | IVIAI NO | <b>Programmes</b> |

| Minor                 | 23MAI301    | Numerical Techniques and Linear Algebra                            | 3   | 0     | 2   | 4       | 100      | -                 |

| Major                 | 23EVT301    | Digital Electronics                                                | 3   | 0     | 0   | 3       | 100      | -                 |

| Major                 | 23EVT302    | Analog Electronics                                                 | 3   | 0     | 0   | 3       | 100      | -                 |

| Multi<br>Disciplinary | 23EVI301    | Data Structures and Algorithms using Python                        | 2   | 0     | 2   | 3       | 100      | -                 |

| Major                 | 23EVL301    | Digital IC Laboratory                                              | 0   | 0     | 3   | 1.5     | 100      | -                 |

| Major                 | 23EVL302    | Analog Electronics Laboratory                                      | 0   | 0     | 3   | 1.5     | 100      | -                 |

| SEC                   | 23ESL301    | Professional Skills 2: Problem solving skills & Logical Thinking 2 | 0   | 0     | 2   | 1       | 100      | All               |

| VAC                   | 23VAT301    | Universal Human Values 2: Understanding Harmony                    | 2   | 1     | 0   | 3       | 100      | All               |

| AEC                   | 23SAL301    | Studio Activities                                                  | 0   | 0     | 2   | -       | -        | All               |

|                       | Total       |                                                                    |     |       |     | 20      | 800      | -                 |

#### **Semester IV**

| Course   | Course Code | Course Title                                                         | Hou | rs/W | eek | Credits | Marks    | Common to  |

|----------|-------------|----------------------------------------------------------------------|-----|------|-----|---------|----------|------------|

| Category | Course Coue | Course Title                                                         | L   | T    | Р   | Cicuits | IVIAI NO | Programmes |

| Minor    | 23MAI401    | Probability Theory and Statistics                                    | 3   | 0    | 2   | 4       | 100      | -          |

| Major    | 23EVT401    | Linear Integrated Circuits                                           | 3   | 0    | 0   | 3       | 100      | -          |

| Major    | 23EVT402    | Signals and systems                                                  | 3   | 1    | 0   | 4       | 100      | -          |

| Major    | 23EVI401    | Fundamentals of VLSI                                                 | 3   | 0    | 2   | 4       | 100      | -          |

| Major    | 23EVT403    | Microprocessors and Microcontrollers                                 | 3   | 0    | 0   | 3       | 100      | -          |

| Major    | 23EVL401    | Microprocessors and Microcontrollers Laboratory                      | 0   | 0    | 3   | 1.5     | 100      | -          |

| Major    | 23EVL402    | Linear Integrated Circuits Laboratory                                | 0   | 0    | 4   | 2       | 100      | -          |

| SEC      | 23ESL401    | Professional Skills 3 :<br>Professional Development and<br>Etiquette | 0   | 0    | 2   | 1       | 100      | All        |

| AEC      | 23SAL401    | Studio Activities                                                    | 0   | 0    | 2   | -       | -        | All        |

|          | Total       |                                                                      |     |      | 15  | 22.5    | 800      | -          |

| Course<br>Category | Course Code | Course Title                                                 | Duration             | Credits | Marks | Common to Programmes |

|--------------------|-------------|--------------------------------------------------------------|----------------------|---------|-------|----------------------|

| SEC                | 23XXXXXX    | Internship - 1 / Community<br>Internship / Skill Development | 2 Weeks -<br>4 Weeks | 1       | 100   | -                    |

#### Semester V

| Course   | Course Code | Course Title                                                               | Но | urs/\ | Veek | Credits | Marks    | Common to  |

|----------|-------------|----------------------------------------------------------------------------|----|-------|------|---------|----------|------------|

| Category | Course Coue | Course ritte                                                               | L  | Т     | Р    | Cieuits | iviai NS | Programmes |

| Major    | 23EVT501    | Control Systems                                                            | 3  | 1     | 0    | 4       | 100      | =          |

| Major    | 23EVT502    | HDL Programming                                                            | 3  | 0     | 0    | 3       | 100      | -          |

| Major    | 23EVT503    | Analog IC Design                                                           | 3  | 0     | 0    | 3       | 100      | -          |

| Major    | 23XXXXX     | Professional Elective – I                                                  | 3  | 0     | 0    | 3       | 100      | -          |

| Major    | 23XXXXX     | Professional Elective – II                                                 | 3  | 0     | 0    | 3       | 100      | -          |

| Major    | 23EVL501    | HDL Programming Laboratory                                                 | 0  | 0     | 3    | 1.5     | 100      |            |

| Major    | 23EVL502    | Analog IC Design Laboratory                                                | 0  | 0     | 3    | 1.5     | 100      | -          |

| SEC      | 23ESL501    | Professional Skills 4:<br>Communication Skills and<br>Interview Essentials | 0  | 0     | 2    | 1       | 100      | All        |

| Project  | 23EVP501    | Reverse Engineering Project                                                | 0  | 0     | 6    | 3       | 100      | All        |

| AEC      | 23SAL501    | Studio Activities                                                          | 0  | 0     | 2    | -       | -        | All        |

|          |             | Total                                                                      | 15 | 1     | 16   | 23      | 900      | -          |

#### Semester VI

| Course   | Course   | O Title                                                          | Но | urs/W | eek | 0       |       | Common to  |

|----------|----------|------------------------------------------------------------------|----|-------|-----|---------|-------|------------|

| Category | Code     | Course Title                                                     | L  | Т     | Р   | Credits | Marks | Programmes |

| Major    | 23EVT601 | Digital IC Design                                                | 3  | 0     | 0   | 3       | 100   |            |

| Major    | 23EVT602 | VLSI Digital Signal Processing                                   | 3  | 0     | 0   | 3       | 100   |            |

| Major    | 23EVT603 | FPGA based System Design                                         | 3  | 0     | 0   | 3       | 100   |            |

| Major    | 23XXXXXX | Professional Elective – III                                      | 3  | 0     | 0   | 3       | 100   |            |

| Major    | 23XXXXXX | Professional Elective – IV                                       | 3  | 0     | 0   | 3       | 100   |            |

| Minor    | 23XXXXXX | Open Elective – I                                                | 3  | 0     | 0   | 3       | 100   |            |

| Major    | 23EVL601 | Digital IC Design Laboratory                                     | 0  | 0     | 3   | 1.5     | 100   |            |

| Major    | 23EVL602 | FPGA based System Design<br>Laboratory                           | 0  | 0     | 3   | 1.5     | 100   |            |

| SEC      | 23ESL601 | Professional Skills 5: Ace and Elevate: Aptitude and Soft Skills | 0  | 0     | 2   | 1       | 100   | All        |

| AEC      | 23SAL601 | Studio Activities                                                | 0  | 0     | 2   | -       | -     | All        |

|          |          | Total                                                            | 18 | 0     | 9   | 22      | 900   |            |

| Course<br>Category | Course Code | Course Title                                                 | Duration             | Credits | Marks |

|--------------------|-------------|--------------------------------------------------------------|----------------------|---------|-------|

| SEC                | 23EVSXXX    | Internship – 2/<br>Research Internship/<br>Skill Development | 2 Weeks –<br>4 Weeks | 1       | 100   |

## Tentative Curriculum for Semester VII to VIII Semester VII

| Course   | Course   | Course Title                           | Но | urs/W | eek  | One dite | Moulso | Common to  |

|----------|----------|----------------------------------------|----|-------|------|----------|--------|------------|

| Category | Code     | Course Title                           | L  | Т     | Р    | Credits  | Marks  | Programmes |

| Major    | 23EVT701 | ASIC Design                            | 3  | 0     | 0    | 3        | 100    |            |

| Major    | 23EVT702 | Verification and Testing               | 3  | 0     | 0    | 3        | 100    |            |

| Major    | 23EVE005 | Professional Elective - V              | 3  | 0     | 0    | 3        | 100    |            |

| Major    | 23EVE006 | Professional Elective - VI             | 3  | 0     | 0    | 3        | 100    |            |

| Minor    | 23EVO002 | Open Elective - II                     | 3  | 0     | 0    | 3        | 100    |            |

| Major    | 23EVL701 | Verification and Testing<br>Laboratory | 0  | 0     | 3    | 1.5      | 100    |            |

| Project  | 23EVP701 | Project Phase - I                      | 0  | 0     | 8    | 4        | 100    |            |

| Total    |          | 15                                     | 0  | 11    | 20.5 | 700      |        |            |

#### **Semester VIII**

| Course Course |          | Course Title       | Но | urs/W | eek | Cradita | Morko | Common to  |

|---------------|----------|--------------------|----|-------|-----|---------|-------|------------|

| Category      | Code     | Course Title       | L  | Т     | Р   | Credits | Marks | Programmes |

| Project       | 23EVP801 | Project Phase – II | 0  | 0     | 12  | 6       | 200   | Project    |

| Internship    | 23EVSXXX | Internship – 3     |    | 8 We  | eks | 4       | 100   |            |

|               |          | Total              | 0  | 0     | 12  | 10      | 300   |            |

**Total Credits: 163.5**

#### **Vertical wise Electives**

|          | Vertical I - Semiconductor Technologies and Packaging Systems |                                                                 |            |   |   |         |       |            |  |  |  |

|----------|---------------------------------------------------------------|-----------------------------------------------------------------|------------|---|---|---------|-------|------------|--|--|--|

| Course   | Course Code                                                   | Course Title                                                    | Hours/Week |   |   | Credits | Marks | Common to  |  |  |  |

| Category | <b>C</b> 04100 <b>C</b> 040                                   | 334133 1113                                                     | L          | T | Р | Ground  | manto | Programmes |  |  |  |

| Major    | 23EVE001                                                      | Advanced MOSFET<br>Modelling                                    | 3          | 0 | 0 | 3       | 100   | -          |  |  |  |

| Major    | 23EVE002                                                      | Compound Semiconductor Devices                                  | 3          | 0 | 0 | 3       | 100   | -          |  |  |  |

| Major    | 23EVE003                                                      | Design of Analog Filters<br>and Signal Conditioning<br>Circuits | 3          | 0 | 0 | 3       | 100   | -          |  |  |  |

| Major    | 23EVE004                                                      | Signal Integrity for High-<br>Speed Design                      | 3          | 0 | 0 | 3       | 100   | -          |  |  |  |

| Major    | 23EVE005                                                      | Electronic Packaging<br>Techniques                              | 3          | 0 | 0 | 3       | 100   | <u>-</u>   |  |  |  |

| Major    | 23EVE006                                                      | Network on Chip                                                 | 3          | 0 | 0 | 3       | 100   | -<br>-     |  |  |  |

|          | Vertical II- Mixed-Signal and System Level Design |                                                  |    |       |     |         |         |            |  |  |  |  |  |  |

|----------|---------------------------------------------------|--------------------------------------------------|----|-------|-----|---------|---------|------------|--|--|--|--|--|--|

| Course   | Course Code                                       | Course Title                                     | Ho | urs/W | eek | Credits | Marks   | Common to  |  |  |  |  |  |  |

| Category | Course Coue                                       | Course Title                                     | L  | T     | P   | Cieuits | IVIAINS | Programmes |  |  |  |  |  |  |

| Major    | 23EVE007                                          | Art of Analog Layout                             | 3  | 0     | 0   | 3       | 100     | -          |  |  |  |  |  |  |

| Major    | 23EVE008                                          | Mixed-Signal Circuit<br>Design                   | 3  | 0     | 0   | 3       | 100     | -          |  |  |  |  |  |  |

| Major    | 23EVE009                                          | Data Converters                                  | 3  | 0     | 0   | 3       | 100     | -          |  |  |  |  |  |  |

| Major    | 23EVE010                                          | Power Management and Clock Distribution Circuits | 3  | 0     | 0   | 3       | 100     | -          |  |  |  |  |  |  |

| Major    | 23EVE011                                          | Radio Frequency IC<br>Design                     | 3  | 0     | 0   | 3       | 100     | -          |  |  |  |  |  |  |

| Major    | 23EVE012                                          | PCB and System Design                            | 3  | 0     | 0   | 3       | 100     | -          |  |  |  |  |  |  |

|          |             | Vertical III - VLSI D                                  | esign | Auto  | matio | n       |         |            |

|----------|-------------|--------------------------------------------------------|-------|-------|-------|---------|---------|------------|

| Course   | Course Code | Course Title                                           | Ho    | urs/W | eek   | Credits | Marks   | Common to  |

| Category | Course Code | Course Title                                           | L     | T     | Р     | Credits | IVIAINS | Programmes |

| Major    | 23EVE013    | Scripting language for VLSI                            | 3     | 0     | 0     | 3       | 100     | -          |

| Major    | 23EVE014    | Algorithms for VLSI                                    | 3     | 0     | 0     | 3       | 100     | -          |

| Major    | 23EVE015    | Physical Design and Automation                         | 3     | 0     | 0     | 3       | 100     | -          |

| Major    | 23EVE016    | Reconfigurable<br>Computing System and<br>Applications | 3     | 0     | 0     | 3       | 100     | -          |

| Major    | 23EVE017    | Machine Learning in<br>VLSI Design                     | 3     | 0     | 0     | 3       | 100     | -          |

| Major    | 23EVE018    | Hardware Security and Cryptography                     | 3     | 0     | 0     | 3       | 100     | -          |

|          | Vertical IV - Low Power and Quantum VLSI Systems |                                                 |    |       |   |          |        |            |  |  |  |  |  |

|----------|--------------------------------------------------|-------------------------------------------------|----|-------|---|----------|--------|------------|--|--|--|--|--|

| Course   | Carres Cada                                      | Corres Title                                    | Но | urs/W |   | Oue dite | Maulea | Common to  |  |  |  |  |  |

| Category | Course Code                                      | Course Title                                    | L  | T     | P | Credits  | Marks  | Programmes |  |  |  |  |  |

| Major    | 23EVE019                                         | Introduction to VLSI Life Cycle                 | 3  | 0     | 0 | 3        | 100    | -          |  |  |  |  |  |

| Major    | 23EVE020                                         | VLSI Technology                                 | 3  | 0     | 0 | 3        | 100    | -          |  |  |  |  |  |

| Major    | 23EVE021                                         | Memory Devices and Circuits                     | 3  | 0     | 0 | 3        | 100    | -          |  |  |  |  |  |

| Major    | 23EVE022                                         | Low Power VLSI Design Techniques                | 3  | 0     | 0 | 3        | 100    | -          |  |  |  |  |  |

| Major    | 23EVE023                                         | System on Chip                                  | 3  | 0     | 0 | 3        | 100    | -          |  |  |  |  |  |

| Major    | 23EVE024                                         | Quantum Technology for<br>Electronics Engineers | 3  | 0     | 0 | 3        | 100    | -          |  |  |  |  |  |

|          | Vertical V - Embedded Intelligence and IoT Technologies |                                     |    |       |     |         |       |            |  |  |  |  |  |

|----------|---------------------------------------------------------|-------------------------------------|----|-------|-----|---------|-------|------------|--|--|--|--|--|

| Course   | Course Code                                             | Course Title                        | Ho | urs/W | eek | Credits | Marks | Common to  |  |  |  |  |  |

| Category | Course Code                                             | Course Title                        | L  | T     | Р   | Credits | Walks | Programmes |  |  |  |  |  |

| Major    | 23EVE025                                                | Embedded Systems                    | 3  | 0     | 0   | 3       | 100   | -          |  |  |  |  |  |

| Major    | 23EVE026                                                | IoT Processor                       | 3  | 0     | 0   | 3       | 100   | -          |  |  |  |  |  |

| Major    | 23EVE027                                                | Embedded System Design with FPGA    | 3  | 0     | 0   | 3       | 100   | -          |  |  |  |  |  |

| Major    | 23EVE028                                                | Embedded Artificial<br>Intelligence | 3  | 0     | 0   | 3       | 100   | -          |  |  |  |  |  |

| Major    | 23EVE029                                                | Data Analytics for IOT              | 3  | 0     | 0   | 3       | 100   | -          |  |  |  |  |  |

| Major    | 23EVE030                                                | Privacy and Security in IOT         | 3  | 0     | 0   | 3       | 100   | -          |  |  |  |  |  |

|          | Dive                           | rsified |       |     |         |          |               |  |

|----------|--------------------------------|---------|-------|-----|---------|----------|---------------|--|

| Course   | Course Title                   | Ноц     | ırs/W | eek | Credits | Marks    | Common to     |  |

| Code     | Course Title                   | L       | Т     | Р   | Credits | IVIAI KS | Programmes    |  |

| 23ECE051 | Computer Architecture          | 3       | 0     | 0   | 3       | 100      | EA,EC,EV      |  |

| 23EEE085 | Industrial Automation          | 3       | 0     | 0   | 3       | 100      | EA,EC,EE,EV   |  |

| 23EEE014 | Automotive Electronics         | 3       | 0     | 0   | 3       | 100      | EA,EC,EE,EV   |  |

| 23MEE008 | PLM for Engineers              | 2       | 0     | 2   | 3       | 100      | Common to all |  |

| 23MEE030 | Principles of Management       | 3       | 0     | 0   | 3       | 100      | EA,EC,EV,ME   |  |

| 23SCE050 | Cybersecurity                  | 3       | 0     | 0   | 3       | 100      | -             |  |

| 23AUE050 | Entrepreneurship Development   | 3       | 0     | 0   | 3       | 100      | Common to all |  |

| 23AUE051 | Design Thinking and Innovation |         | 0     | 0   | 3       | 100      | Common to all |  |

| 23ITE047 | Intellectual Property Rights   | 3       | 0     | 0   | 3       | 100      | Common to all |  |

|                | Open Elective    |     |       |     |         |       |            |  |  |  |  |  |

|----------------|------------------|-----|-------|-----|---------|-------|------------|--|--|--|--|--|

| Course<br>Code | Course Title     | Ηοι | ırs/W | eek | Credits | Marks | Common to  |  |  |  |  |  |

|                |                  | L   | Т     | Р   |         |       | Programmes |  |  |  |  |  |

| 23EVO001       | Microelectronics | 3   | 0     | 0   | 3       | 100   | -          |  |  |  |  |  |

| 23EVO002       | Nanoelectronics  | 3   | 0     | 0   | 3       | 100   | -          |  |  |  |  |  |

# SEMESTER I

| Course Code:23VAL101 Course Title: Induction Program (Common to all B.E / B.Tech Programmes) |                             |               |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|-----------------------------|---------------|--|--|--|--|--|

| Course Category: VAC                                                                         | Course Level: Introductory  |               |  |  |  |  |  |

| Duration: 3 weeks                                                                            | Mandatory Non-Credit Course | Max Marks:100 |  |  |  |  |  |

#### Pre-requisites

> NIL

#### **Course Objectives**

The course is intended to:

- Explain various sources available to meet the needs of self, such as personal items and learning resources

- 2. Explain various career opportunities, opportunity for growth of self and avenues available in the campus

- 3. Explain the opportunity available for professional development

- 4. Build universal human values and bonding amongst all the inmates of the campus and the society.

#### **List of Activities:**

- History of Institution and Management: Overview on NIA Educational Institutions –Growth of MCET – Examination Process –OBE Practices –Code of Conduct – Centre of Excellence.

- 2. Lectures, interaction sessions and Motivational Talks by Eminent people, Alumni, Employer and Industry Experts

- 3. Familiarisation of Department / Branch: HoD's & Senior Interaction- Department Association

- 4. Universal Human Value Modules: Aspirations and concerns, Self Management, Relations Social and Natural Environment.

- 5. Orientation on Professional Skills Courses

- 6. Proficiency Modules: Mathematics, English, Physics and Chemistry

- 7. Introduction to various Chapters, Cells, Clubs and its events

- 8. Creative Arts: Painting, Music and Dance

- 9. Physical Activity: Games, Sports and Yoga

- 10. Group Visits: Visit to local area and Campus Tour

| Course Outcomes                                                                                                                                           | Cognitive  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| At the end of this course, students will be able to:                                                                                                      | Level      |

| CO1 : Explain various sources available to meet the needs of self, such as personal items and learning resources through visit to local areas and campus  | Understand |

| CO2: Explain various career opportunities and avenues available in the campus through orientation sessions                                                | Understand |

| CO3: Explain the opportunity available for professional development through professional skills, curricular, co-curricular and extracurricular activities | Understand |

| CO4: Build universal human values and bonding amongst all the inmates of the campus and society for having a better life                                  | Apply      |

| СО  | PO1 | PO2 | PO3 | PO4 | PO5 | P06 | PO7 | PO8 | PO9 | P01 | PO1 | PO1 | PSO | PSO |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CO1 | 1   | ,   | 1   | 1   | 1   | 1   | 1   | 2   | 1   | 2   | 1   | -   | ,   | -   |

| CO2 | 1   | 1   | ı   | ı   | ı   | 1   | ı   | 2   | 1   | 2   | 1   | -   | 1   | -   |

| CO3 | 1   | -   | -   | -   | -   | -   | -   | 2   | 1   | 2   | -   | -   | -   | -   |

| CO4 | 2   | 1   | 1   | 1   | 1   | 1   | 1   | 2   | 1   | 2   | 1   | -   | 1   | -   |

High: 3, Medium: 2, Low: 1

#### Text Book(s):

T1. Reading material, Workbook prepared by PS team of the college

#### Reference Book(s):

- R1. Sean Covey, "Seven habits of highly effective teenagers", Simon & Schuster Uk, 2004.

- R2. Vethathiri Maharishi Institute For Spiritual and Intuitional Education, aliyar, "value educat harmonious life (Manavalakalai Yoga)", Vethathri Publications, Erode, 2010.

- R3. Dr.R. Nagarathna, Dr.H.R. Nagendra, "Integrated approach of yoga therapy for positive Swami Vivekananada Yoga Prakashana Bangalore, 2008 Ed.

- 1. https://youtube.com/playlist?list=PLYwzG2fd7hzc4HerTNkc3pS\_lvcCfKznV

- 2. https://www.youtube.com/watch?v=P4vjfEVk&list=PLWDeKF97v9SO0frdgmpaghDMjkom1

- 3. https://fdp-si.aicte-india.org/download/AboutSIP/About%20SIP.pdf

| Course Code: 23ENI101   |            | itle: Communication Skills I<br>n to all B.E/B.Tech Programmes) |               |  |  |  |  |  |

|-------------------------|------------|-----------------------------------------------------------------|---------------|--|--|--|--|--|

| Course Category: AEC    |            | Course Level: Introductory                                      |               |  |  |  |  |  |

| L:T:P(Hours/Week) 2:0:2 | Credits: 3 | Total Contact Hours:60                                          | Max Marks:100 |  |  |  |  |  |

#### **Course Objectives**

The course is intended to impart formal and informal language effectively and accurately in various real-life contexts on par with B1 level of CEFR Scale.

Module I 20 Hours

**Grammar:** Synonyms & Antonyms -Tense forms - Modals - Passives — Reported Speech — Comparatives and Descriptive adjectives.

**Listening:** Listening for gist and specific information - Listening to past events, experiences and job preferences - Listening to descriptions of monuments - Listening for excuses - Listening to description: transportation systems and public places.

**Speaking:** Introducing oneself - Exchanging personal information - Effective Conversations: Role Play Situations (Describing personality traits - Describing landmarks, monuments and festivals - Making polite requests and excuses - Discussing facts - Asking for and giving information - Expressing wishes - Talking about lifestyle changes - Talking about transportation and its problems - Describing positive and negative features of things and places - Making comparisons)

**Reading:** Skimming and Scanning - Reading Comprehension - Reading and comprehending online posts and emails – Case Studies

**Writing:** Letter writing (Permission letters - Online cover letter for job applications) - Instructions - Recommendations - Write a blog (General) - Report Writing (Industrial Visit Report and Event Reports) - formal and informal emails.

Module II 20 Hours

**Grammar:** Sequence adverbs - Phrasal verbs - Relative clauses – Imperatives - Infinitives - Conditionals.

**Listening:** Listening to review of food items - Listening to results of surveys- Listening to motivational talks & podcasts

**Speaking:** Expressing likes and dislikes - Describing a favorite snack - Giving advices and suggestions - Speculating about past and future Events – Group Discussion

**Reading:** Reading different expository texts - Reading to factual texts - Print and online media-Reading Comprehension

**Writing:** Process Descriptions – Email Writing (Requesting for information) - Reviewing Movie – Social media feeds/posts (Any Social Media)

- 1. Mini Presentation and Picture Prompt Discussion

- 2. Debate Tournament

- 3. Listening, Mind Mapping & Summarization

- 4. Listening to Stories and Providing the Innovative Climax

- 5. Reading Comprehension

- 6. Writing Interpretation of Visuals

| Course Outcomes                                                                                                                                                   | Cognitive |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| At the end of this course, students will be able to:                                                                                                              | Level     |

| CO 1 : Utilize the basic English grammar and vocabulary to acquire professional communication skills.                                                             | Apply     |

| CO 2 : Develop listening and speaking skills through classroom activities based on listening comprehension, recapitulation, interpretation and debate on the same | Apply     |

| CO 3 : Read and write social media posts and comments                                                                                                             | Apply     |

| CO 4 : Perform as a member of a team and engage in individual presentation                                                                                        | Apply     |

| CO  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | P07 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | -   | -   | -   | -   | -   | -   | -   | -   | -   | 3    | -    | -    | -    | -    |

| CO2 | -   | -   | -   | -   | -   | -   | -   | -   | -   | 3    | -    | -    | -    | -    |

| CO3 | -   | -   | -   | -   | -   | -   | -   | -   | -   | 3    | -    | -    | -    | -    |

| CO4 | -   | -   | -   | -   | -   | -   | -   | -   | 2   | 3    | -    | -    | -    | -    |

High-3; Medium-2;Low-1

#### Textbooks:

- T1. Jack C. Richards, Jonathan Hull, and Susan Proctor, "Interchange Student's book 2", 5<sup>th</sup>Edition, Cambridge University Press, South Asia Edition, 2022.

- T2. Jack C. Richards, Jonathan Hull, and Susan Proctor, "Interchange Student's Book 1", 5th Edition, Cambridge University Press, South Asia Edition, 2022.

#### Reference Book(s):

- R1. David Bohlke, Jack C. Richards, "Four Corners", 2<sup>nd</sup> Edition, Cambridge University Press,2018.

- R2. Adrian Doff, Craig Thaine, Herbert Puchta, Jeff Stranks, Peter Lewis-Jones, Graham Burton, Empower B1 Student's Book, Cambridge University Press, 2020.

- R3. Raymond Murphy, "Intermediate English Grammar" 30<sup>th</sup> Edition, Cambridge University Press,2022.

- 1. https://speakandimprove.com/

- 2. https://writeandimprove.com/

- 3. https://www.cambridgeenglish.org/exams-and-tests/linguaskill/

| Course Code: 23MAI102   |            | se Title: Matrices and Calculus<br>nmon to AU, EA, EC, EE, EV & ME) |               |  |  |  |  |

|-------------------------|------------|---------------------------------------------------------------------|---------------|--|--|--|--|

| Course Category: Minor  |            | Course Level: Introductory                                          |               |  |  |  |  |

| L:T:P(Hours/Week)3:0 :2 | Credits: 4 | Total Contact Hours:75                                              | Max Marks:100 |  |  |  |  |

#### **Course Objectives:**

The course is intended to impart knowledge on the use of matrix algebra techniques for practical applications, familiarize with differential calculus and acquire knowledge of mathematical tools to evaluate multiple integrals.

Module I 23 Hours

#### **Matrices**

Definitions and examples of symmetric, skew symmetric and orthogonal matrices - Eigenvalues and Eigenvectors - Properties of Eigenvalues and Eigenvectors-Diagonalization of matrices through orthogonal transformation - Cayley-Hamilton Theorem (without proof) - verification problems and properties - Transformation of quadratic forms to canonical forms through orthogonal transformation.

#### **Differential and Integral Calculus**

Curvature – Radius of curvature – Centre of curvature - Circle of curvature - Evolutes and Involutes - Evaluation of definite and improper integrals - Beta and Gamma functions – Properties and applications.

#### **Multivariable Differentiation I**

Limit – continuity - Mean value theorems and partial derivatives - Taylor's series and Maclaurin's series – Jacobian of functions of several variables.

Module II 22 Hours

#### **Multivariable Differentiation II**

Maxima, Minima and saddle points of functions of several variables - Method of Lagrange's multipliers.

#### **Multiple Integral**

Multiple Integration: Double integrals - Change of order of integration in double integrals - Change of variables (Cartesian to polar, Cartesian to spherical and Cartesian to cylindrical) - Triple integrals - Applications: Finding areas and volumes.

#### **Ordinary Differential Equations Of Second and Higher Orders**

Second and higher order linear differential equations with constant coefficients – Second order linear differential equations with variable coefficients (Cauchy - Euler equation, Legendre's equation) – Method of variation of parameters – Solution of first order simultaneous linear ordinary differential equations

- 1. Introduction to MATLAB.

- 2. Rank of matrix and solution of system of linear algebraic equations.

- 3. Finding Eigen values and Eigen vectors of a matrix.

- 4. Solving ordinary differential equation.

- 5. Gram Schmidt Procedure.

- 6. Finding Maxima, Minima of a function.

| Course Outcomes                                                                                               | Cognitive Level |

|---------------------------------------------------------------------------------------------------------------|-----------------|

| At the end of this course, students will be able to:                                                          |                 |

| CO1: Determine the canonical form of a quadratic form using orthogonal transformation.                        | Apply           |

| CO2: Identify the evolute of a curve and solve the improper integrals using beta gamma functions.             | Apply           |

| CO3: Examine the extreme value of multivariate functions.                                                     | Apply           |

| CO4: Evaluate the area and volume using multiple integrals and solve the higher order differential equations. | Apply           |

| CO5: Demonstrate the understanding of calculus concepts through modern tools.                                 | Apply           |

| СО  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | 3   | 2   | -   | -   | -   | -   | -   | -   | -   | -    | -    | 1    | -    | -    |

| CO2 | 3   | 2   | -   | -   | -   | -   | -   | -   | -   | -    | -    | 1    | -    | -    |

| CO3 | 3   | 2   | -   | -   | -   | -   | -   | -   | -   | -    | -    | 1    | -    | -    |

| CO4 | 3   | 2   | -   | -   | -   | -   | -   | -   | -   | -    | -    | •    | -    | -    |

| CO5 | -   | -   | -   | -   | 3   | -   | -   | -   | -   | -    | 1    | 1    | -    | =    |

High-3; Medium-2;Low-1

#### Text Book(s):

- T1. Erwinkreyzig, Advanced Engineering Mathematics, 9th edition, John Wiley& Sons, 2006.

- T2. Veerarajan T., Engineering Mathematics for first year, 3rd edition, Tata McGraw-Hill,

#### Reference Book(s):

- R1. G.B.Thomas and R.L Finney, Calculus and Analytic Geometry, 9<sup>th</sup> edition, Pearson, Reprint, 2002.

- R2. B.S.Grewal, Higher Engineering Mathematics, Khanna Publishers, 36<sup>th</sup> Edition, 2010.

- R3. P. Sivaramakrishna Das , C. Vijayakumari , Engineering Mathematics, Pearson India, 2017.

- 1. https://nptel.ac.in/courses/111107112

- 2. https://nptel.ac.in/courses/111104031

| Course Code: 23CHI101     |            | e: Chemistry for Electrical Scier<br>o EC, EE & EV) | nces          |  |  |  |  |  |  |

|---------------------------|------------|-----------------------------------------------------|---------------|--|--|--|--|--|--|

| Type of Course: Minor     | Course Lev | Course Level: Introductory                          |               |  |  |  |  |  |  |

| L:T:P (Hours/Week) 3: 0:2 | Credits:4  | Total Contact Hours:75                              | Max Marks:100 |  |  |  |  |  |  |

#### **Course Objectives**

The course is intended to impart the knowledge of chemistry involved in Electrochemistry, Corrosion and its control, Spectroscopic technique, Fuels and Nanomaterials.

Module: I 23 Hours

#### **Electrochemistry and Batteries:**

Electrochemistry - Basic terminologies - Potentiometric titration – Nernst equation – Batteries – Types and Characteristics, Construction, working and applications - Lead –Acid battery, Lithiumion battery – Fuel cells - Construction, working and applications – Hydrogen Oxygen fuel cell.

#### **Corrosion and its Control:**

Corrosion – Dry and Wet corrosion – Mechanism of electrochemical corrosion – Galvanic corrosion and Concentration cell corrosion, Factors influencing corrosion. Corrosion Control methods – Cathodic protection methods, Metallic coating – Galvanizing, Tinning – Chrome plating and Electroless plating of Nickel

#### **Spectroscopic Techniques:**

Spectroscopy- Electromagnetic spectrum, Absorption and Emission spectroscopy – Relationship between absorbance and concentration – Derivation of Beer-Lambert's law (problems).

Module: II 22 Hours

#### **Spectroscopic Techniques:**

UV - Visible Spectroscopy, Atomic Absorption Spectroscopy, Flame photometry - Principle, Instrumentation, and applications.

#### **Biofuels and Lubricants:**

Biomass - Biogas - Constituents, manufacture and uses. General outline of fermentation process - manufacture of ethyl alcohol by fermentation process. Combustion - Calorific values - Gross and Net calorific value - Problems based on calorific value. Lubricants - Classification of lubricants - Properties of liquid lubricants and their significance - Greases - Common grease types and properties. Components of grease – Base oil, additives and thickener.

#### **Synthesis and Applications of Nano Materials:**

Introduction - Difference between bulk and Nano materials - size dependent properties. Nano scale materials - Particles, clusters, rods, and tubes. Synthesis of Nanomaterials: Sol-Gel process, Electro deposition, Hydrothermal methods. Applications of Nano materials in Electronics, Energy science and Medicines. Risk and future perspectives of nano materials.

#### **LIST OF EXPERIMENTS: (Any 6 experiments)**

30 Hours

- 1. Estimation of Fe<sup>2+</sup> by potentiometric titration.

- 2. Determination of corrosion rate by weight loss method.

- 3. Estimation of iron in water by spectrophotometry

- 4. Determination of Cloud and Pour Point.

- 5. Green Synthesis of Silver Nanoparticles by Neem leaf.

- 6. Conductometric titration of strong acid against strong base.

- 7. Determination of strength of acid by pH metry.

| Course Outcomes                                                                                                                                                                                               | Cognitive  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| At the end of this course, students will be able to:                                                                                                                                                          | Level      |  |

| CO1: Understand and explain the chemistry involved in Electrochemistry, Corrosion, Spectroscopic techniques, Fuels and Nanomaterials.                                                                         | Understand |  |

| CO2: Apply the acquired knowledge of chemistry to solve the Engineering problems.                                                                                                                             | Apply      |  |

| CO3: Analyze the Engineering problems through the concept of Electro chemistry, Spectroscopic techniques, Fuels, and Nanomaterials.                                                                           | Apply      |  |

| CO4: Apply the knowledge of chemistry to investigate Engineering materials by volumetric and instrumental methods and analyze, interpret the data to assess and address the issues of Environmental Pollution | Evaluate   |  |

#### **Course Articulation Matrix**

| СО  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | -   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO2 | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO3 | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO4 | -   | -   | -   | 3   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

#### Text book(s):

- **T1.** Jain and Jain, Engineering Chemistry, 17<sup>th</sup> Edition, Dhanpat Rai Publishing Company, New Delhi, 2018.

- T2. Wiley Engineering Chemistry, 2<sup>nd</sup> Edition, Wiley India Pvt Ltd, New Delhi, 2011.

#### Reference Book(s):

- R1. Dara S. S and Umare S. S., A textbook of Engineering Chemistry, 12<sup>th</sup> Edition, S. Chand & Co Ltd, New Delhi, 2014.

- **R2**. V. R. Gowariker, N. V. Viswanathan and Jayadev Sreedhar, Polymer Science,4<sup>th</sup> Edition New Age International(P) Ltd, Chennai ,2021.

- **R3**. Jeffery G. H., Bassett. J., Mendham J and Denny R. C., Vogel's Textbook of Quantitative Chemical Analysis, 5<sup>th</sup> Edition Oxford, ELBS, London, 2012.

- 1. http://nptel.ac.in/courses/122101001/downloads/lec.23.pdf

- 2. https://nptel.ac.in/courses/104106075/Week1/MODULE%201.pdf

- 3. https://nptel.ac.in/courses/103102015/

| Course Code: 23ECT101    | Cour      | course Title: Electron Devices (Common to EA ,EC & EV) |               |  |  |  |  |

|--------------------------|-----------|--------------------------------------------------------|---------------|--|--|--|--|

| Course Category: Major   |           | Course Level: Introductory                             |               |  |  |  |  |

| L:T:P(Hours/Week)3: 0: 0 | Credits:3 | Total Contact Hours:45                                 | Max Marks:100 |  |  |  |  |

#### **Course Objective:**

The course is intended to impart knowledge of basic electronic devices such as diodes, Bipolar junction Transistors and Field effect transistors.

Module I 23 Hours

**Semiconductor Diode:** PN junction - forward and reverse bias conditions. V-I Characteristics and its Temperature dependence – Diode specifications - Diode Resistance – Diode junction Capacitance – Transition and Diffusion capacitances - Rectifiers - Clipper - Clamper

**Special Diodes:** Zener diode - Characteristics of Zener diode - Avalanche and Zener breakdown - Application of Zener diode :Voltage regulator - Varactor diode, Tunnel diode, Light emitting diodes - Photo diodes

**Bipolar Junction Transistors**: Bipolar Junction Transistor and its types: NPN and PNP Transistor - Transistor operation - Configurations of BJT : Input and output characteristics of CE, CB and CC configurations - Transistor as a Switch and Amplifier.

Module II 22 Hours

**Field Effect Transistors:** JFET and its types, construction and operation of n- channel and p-channel JFETs – characteristics curves – FET applications – Comparison of BJT and JFET **MOSFETS and Power Devices:** MOSFETs: Depletion MOSFETs and Enhancement MOSFETs – construction and operation - Drain and Transfer characteristics - Differences between JFETs and MOSFETs – Precaution in handling MOSFETs - MOSFET as a switch.

Construction, operation and characteristics of SCR, DIAC, TRIAC, Power transistor and IGBT

| Course Outcomes                                                                                                                                  | Cognitive Level |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| At the end of this course, students will be able to:                                                                                             |                 |  |  |

| CO 1: Understand and explain the construction and characteristics of PN junction diode, special diodes, BJTs, FETs and Power devices.            | Understand      |  |  |

| CO 2: Identify a suitable electronic device and develop appropriate circuit for the given application.                                           | Analyze         |  |  |

| CO 3: Engage in independent study as a member of a team and make an effective oral presentation on the applications of various Electron devices. | Apply           |  |  |

| СО  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | P07 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | -   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO2 | -   | 3   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO3 | 3   | -   | -   | -   | -   | -   | -   | -   | 2   | 2    | -    | 1    | 1    | -    |

High-3; Medium-2; Low-1

#### **Text Book:**

T1. Millman J., Halkias C. C. "Electronic Devices and Circuits ", Tata McGraw Hill, New Delhi, 2011.

#### Reference Book(s):

- R1. Salivahanan.S, Suresh kumar.N and Vallavaraj.A, "Electronic Devices and Circuits", Second Edition, TMH, New Delhi, 2008.

- R2. Robert Boylestad and Louis Nashelsky, "Electron Devices and Circuit Theory", Pearson Prentice Hall, Tenth Edition, 2008.

- R3. Streetman Ben G. and Banerjee Sanjay, "Solid State Electronic devices", PHI, Sixth Edition, 2006

- R4. David A. Bell, "Electronic Devices and Circuits", Oxford University Press, Fifth Edition, 2008

- 1. http://nptel.ac.in/video.php?subjectId=117103063

- 2. http://nptel.ac.in/video.php?subjectId=117106091

- 3. www.youtube.com/watch?v=Wf19II0ts84

| Course Code: 23ADT001      |           | se Title: C Programming<br>mon to CE, EA, EC, EE & EV) |               |  |  |  |  |

|----------------------------|-----------|--------------------------------------------------------|---------------|--|--|--|--|

| Course Category: Multi-dis | ciplinary | Course Level: Introductory                             |               |  |  |  |  |

| L:T:P(Hours/Week)3: 0: 0   | Credits:3 | Total Contact Hours:45                                 | Max Marks:100 |  |  |  |  |

#### **Course Objectives:**

The course helps to understand the structured and procedural programming skills. The major objective is to provide students with understanding of code organization and functional hierarchical decomposition using complex data types.

Module I 22 Hours

**Basics Of Computer Organization:** Generation and Classification of Computers – Basic Organization of a Computer – Software development life cycle – Problem Solving Techniques, Algorithm, Pseudo code and Flow Chart.

**Introduction To C Programming:** Introduction – Structure of a C program – Keywords – Identifiers – Constants – Variables – Data Types – Operators and Expressions – Formatted & Unformatted I/O functions – Decision statements – Loop control statements.

**Arrays:** Characteristics – Declaration-One-dimensional array, Two-dimensional arrays

Module II 23 Hours

**Functions:** Declaration & Definition of function – Built in function – User defined function -Types of functions – Call by value & reference.

**Strings and Pointers:** Formatting strings – String handling functions. Pointers: Features and Types of pointers – Arithmetic operations with pointers–Pointers and Arrays- Array of Pointers-Pointers and Strings

**Structures and Union:** Structures: Features – Operations on Structures – Array of structures – Pointers to Structures - Unions-Union of Structures.

| Course Outcomes                                                                                                                                           | Cognitive |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| At the end of this course, students will be able to:                                                                                                      | Level     |

| CO1: Correlate the fundamental concepts of computer organization such as architectures of the processors and project management for real time application | Apply     |

| CO2:Infer the fundamental concepts of programming, such as variables, data types and control structures for real time problems                            | Analyze   |

| CO3:Apply programs solving skills and knowledge of C programmingconstructs to solve the given one dimensional and two dimensional datasets                | Apply     |

| CO4: Build a modules to solve the given application using functions                                                                                       | Apply     |

| CO5:Develop a program by accessing the address of the variable using pointers and manipulation of characters using string handling functions              | Apply     |

| CO6: Test the performance of the students by group assignments and projects on real time problems                                                         | Evaluate  |

| СО  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | 2   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO2 | -   | 3   | -   | -   | 2   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO3 | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO4 | 2   | -   | 1   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO5 | 3   | -   | -   | 1   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO6 | -   | 1   | -   | 3   | 2   | -   | -   | -   | 2   | -    | -    | 2    | -    | -    |

High-3; Medium-2; Low-1

#### Text Book(s):

- T1. Ashok N.Kamthane, Amit.N.Kamthane, Programming in C, 3<sup>rd</sup> Edition, Pearson Education, 2015.

- T2. Deitel H M and Deitel P J, "C How to Program", Prentice Hall, 2013.

#### Reference Book(s):

- R1. Ajay Mittal, "Programming in C-A Practical Approach", 3<sup>rd</sup> Edition, Pearson Education, 2010.

- R2. Yashavant P.Kanetkar," Let Us C", 16th Edition, BPB Publications, 2018.

- R3. Herbert Schildt, "C The Complete Reference", Tata McGraw Hill, 2010.

- R4. S Gottfried Byron, "Programming With C", Tata McGraw Hill, 2011.

- NPTEL course content on Introduction To Programming In https://onlinecourses.nptel.ac.in/noc22\_cs40

- 2. Complete guide on Learn C programming: http://www.cprogramming.com/

- 3. Complete reference manual on C programming: http://www.c4learn.com/

| Course Code:23ADL          | 004            | Course Title: C Programming Laboratory (Common to CE,EA,EC,EE & EV) |                            |               |  |  |  |  |

|----------------------------|----------------|---------------------------------------------------------------------|----------------------------|---------------|--|--|--|--|

| Course Category: M         | ulti-disciplin | ary                                                                 | Course Level: Introductory |               |  |  |  |  |

| L:T:P(Hours/Week)<br>0:0:3 | Credits:1.5    | Total Contact Ho                                                    | ours:45                    | Max Marks:100 |  |  |  |  |

#### **Course Objectives**

The course introduces students to the practical knowledge of programming using C programming language as an implementation tool. It aims at providing students with understanding of programming essentials used within the framework of imperative and structural programming paradigms.

#### **List of Experiments:**

- 1. Implement basic C programs using data types

- 2. Implement programs using Operators and Expressions

- 3. Develop Programs using Branching statements

- **4.** Implement Programs using Control Structures

- 5. Develop programs using Arrays

- **6.** Implement programs using Functions

- 7. Implement programs using String Operations

- **8.** Develop programs using Pointers

- 9. Implement programs using Structures

- 10. Develop programs using Union

| Course Outcomes                                                                                                                              | Cognitive |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| At the end of this course, students will be able to:                                                                                         | Level     |

| CO1:Write programs using appropriate programming constructs.                                                                                 | Apply     |

| CO2:Apply programs solving skills and knowledge of C programming constructs to solve the given one dimensional and two dimensional dataset   | Apply     |

| CO3:Develop a program by accessing the address of the variable using pointers and manipulation of characters using string handling functions | Analyze   |

| CO4:Evaluate modular programming techniques to break down complex programs into smaller and manageable modules                               | Evaluate  |

| СО  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | P07 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | 2   | -   | -   | -   | 3   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO2 | 3   | -   | -   | -   | 3   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| СОЗ | -   | 2   | -   | -   | 3   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| CO4 | -   | -   | -   | 3   | 3   | -   | -   | ı   | -   | -    | -    | 1    | -    | -    |

High-3; Medium-2; Low-1

#### Text Book(s):

- T1. Ashok N.Kamthane, Amit.N.Kamthane, Programming in C, 3<sup>rd</sup> Edition, Pearson education, 2015.

- T2. Deitel H M and Deitel P J, "C How to Program", Prentice Hall, 2013.

#### Reference Book(s):

- R1. Ajay Mittal, "Programming in C-A Practical Approach", 3<sup>rd</sup> Edition, Pearson Education, 2010.

- R2. Yashavant P.Kanetkar, "Let Us C", 16th Edition, BPB Publications, 2018.

- R3. Herbert Schildt, "C The Complete Reference", Tata McGraw Hill, 2010.

- C programming resources: https://electronicsforu.com/resources/15-free-c-programmingebooks

- 2. C programming tutorials: https://www.fromdev.com/2013/10/c-programming-tutorials.html

- 3. C Manual: https://books.goalkicker.com/CBook

| Course Code: 23VAL102   |           | rse Title: Wellness for Students<br>nmon to all B.E/B.Tech Programmes) |               |  |  |  |  |

|-------------------------|-----------|------------------------------------------------------------------------|---------------|--|--|--|--|

| Course Category: VAC    |           | Course Level: Introductory                                             |               |  |  |  |  |

| L:T:P(Hours/Week) 0:0:2 | Credits:1 | Total Contact Hours:30                                                 | Max Marks:100 |  |  |  |  |

#### **Course Objectives:**

The course is intended to impart knowledge on setting SMART goals for academic, career and life, applying time management techniques, articulating the importance of wellness for success in life and understanding the dimensions of wellbeing and relevant practices.

Module I 15 Hours

**GOAL SETTING** Understanding Vision and mission statements - Writing personal mission statements - 'Focus' as a way of life of most successful people. Clarifying personal values, interests and orientations - Awareness of opportunities ahead - Personal SWOT analysis - Principles driving goal setting: Principle of response and stimuli, Circle of influence and circle of concern, What you see depends on the role you assume. Potential obstacles to setting and reaching your goals - Five steps to goals setting: SMART goals, Inclusive goals, Positive stretch, Pain vs gain, Gun-point commitment.

**TIME MANAGEMENT - TOOLS AND TECHNIQUES** Importance of planning and working to time. Pareto 80-20 principle of prioritization – Time quadrants as a way to prioritize weekly tasks – The glass jar principle - Handling time wasters – Assertiveness, the art of saying 'NO' – Managing procrastination.

**CONCEPT OF WELLNESS** – impact of absence of wellness - Wellness as important component to achieve success. Wellbeing as per WHO - Dimensions of Wellbeing: Physical, Mental, Social, Spiritual – indicators and assessment methods

Module II 15 Hours

**Simplified Physical Exercises**. Fitness as a subset of Wellness – health related physical fitness - skill related physical fitness. Joint movements, Warm up exercises, simple asanas, WCSC simplified exercises.

#### PRACTICES FOR MENTAL WELLNESS

**Meditation:** Mind and its functions - mind wave frequency – Simple basic meditation – WCSC meditation and introspection tables. Greatness of friendship and social welfare – individual, family and world peace – blessings and benefits.

**Food & sleep for wellness:** balanced diet - good food habits for better health (anatomic therapy) – hazards of junk food - food and the gunas.

#### **PUTTING INTO PRACTICE**

Practicals: Using the weekly journal – Executing and achieving short term goals – Periodic reviews.

| Course Outcomes                                                                             | Cognitive Level |

|---------------------------------------------------------------------------------------------|-----------------|

| At the end of this course, students will be able to:                                        |                 |

| CO 1:Set well-articulated goals for academics, career, and personal aspirations             | Apply           |

| CO 2: Apply time management techniques to complete planned tasks on time                    | Apply           |

| CO 3:Explain the concept of wellness and its importance to be successful in career and life | Apply           |

| CO 4:Explain the dimensions of wellness and practices that can promote wellness             | Apply           |

| CO 5: Demonstrate the practices that can promote wellness                                   | Valuing         |

| СО  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| CO1 | -   | -   | -   | -   | -   | -   | -   | -   | 1   | 1    | -    | 1    |

| CO2 | -   | -   | -   | -   | -   | -   | -   | -   | 1   | -    | 1    | 1    |

| CO3 | -   | -   | -   | -   | -   | -   | -   | -   | 1   | -    | -    | 1    |

| CO4 | -   | -   | -   | -   | -   | -   | -   | -   | 1   | -    | -    | 1    |

| CO5 | -   | -   | -   | -   | -   | 1   | 1   | -   | 1   | -    | -    | 1    |

High-3; Medium-2;Low-1

#### Text Book(s):

- T1. Reading material, workbook and journal prepared by PS team of the college Reference Book(s):

- R1. Stephen R Covey, "First things first", Simon & Schuster UK, Aug 1997

- R2. Sean Covey, "Seven habits of highly effective teenagers", Simon & Schuster UK, 2004.

- R3. Vethathiri Maharishi Institute for Spiritual and Intuitional Education, Aliyar, "Value education for harmonious life (Manavalakalai Yoga)", Vethathiri Publications, Erode, I Ed. (2010).

- R4. Dr. R. Nagarathna, Dr. H.R. Nagendra, "Integrated approach of yoga therapy for positive health", Swami Vivekananda Yoga Prakashana, Bangalore, 2008 Ed.

- R5. Tony Buzan, Harper Collins, "The Power of Physical Intelligence English"

| Course Code: 23VAT101         |           | itle: HERITAGE OF TAMILS  n to all B.E/B.Tech Programmes) |               |  |  |  |  |

|-------------------------------|-----------|-----------------------------------------------------------|---------------|--|--|--|--|

| Course Category: VAC          |           | Course Level: Introductory                                |               |  |  |  |  |

| L:T:P (Hours/Week)<br>1: 0 :0 | Credit: 1 | Total Contact Hours: 15                                   | Max Marks:100 |  |  |  |  |

#### Pre-requisites

> NIL

#### **Course Objectives**

மாணவர்கள் இப்பாடத்தை கற்றலின் மூலம்

- CO.1 மொழி மற்றும் இலக்கியம், பாறை ஓவியங்கள் முதல் நவீன ஓவியங்கள் வரை சிற்பக் கலை, நாட்டுப்புறக் கலைகள் மற்றும் வீர விளையாட்டுகள், திணைக் கோட்பாடுகள் மூலம் தமிழர் மரபை அறிந்து கொள்ள இயலும்.

- CO.2இந்திய தேசிய இயக்கம் மற்றும் இந்திய பண்பாட்டிற்குத் தமிழர்களின் பங்களிப்பை அறிந்து கொள்ள இயலும்.

#### தமிழர் மரபு

#### அலகு 1 – மொழி மற்றும் இலக்கியம்

3

இந்திய மொழிக் குடும்பங்கள் – திராவிட மொழிகள் – தமிழ் ஒரு செம்மொழி – தமிழ் செவ்விலக்கியங்கள் – சங்க இலக்கியத்தின் சமயச் சார்பற்ற தன்மை – சங்க இலக்கியத்தில் பகிர்தல் அறம் – திருக்குறளில் மேலாண்மைக் கருத்துக்கள் – தமிழ்க் காப்பியங்கள், தமிழகத்தில் சமண பௌத்த சமயங்களின் தாக்கம் – பக்தி இலக்கியம், ஆழ்வார்கள் மற்றும் நாயன்மார்கள் – சிற்றிலக்கியங்கள் – தமிழில் நவீன இலக்கியத்தின் வளர்ச்சி – தமிழ் இலக்கிய வளர்ச்சியில் பாரதியார் மற்றும் பாரதிதாசன் ஆகியோரின் பங்களிப்பு.

#### அலகு 2 – மரபு – பாறை ஓவியங்கள் முதல் நவீன ஓவியங்கள் வரை – சிற்பக் கலை 3

நடுகல் முதல் நவீன சிற்பங்கள் வரை – ஐம்பொன் சிலைகள் – பழங்குடியினர் மற்றும் அவர்கள் தயாரிக்கும் கைவினைப் பொருட்கள், பொம்மைகள் – தேர் செய்யும் கலை – சுடுமண் சிற்பங்கள் – நாட்டுப்புறத் தெய்வங்கள் – குமரிமுனையில் திருவள்ளுவர் சிலை – இசைக் கருவிகள் – மிருதங்கம், பறை, வீணை, யாழ், நாதஸ்வரம் – தமிழர்களின் சமூக பொருளாதார வாழ்வில் கோவில்களின் பங்கு.

#### அலகு 3 – நாட்டுப்புறக் கலைகள் மற்றும் வீர விளையாட்டுகள்

3

தெருக்கூத்து, கரகாட்டம், வில்லுப்பாட்டு, கணியான் கூத்து, ஒயிலாட்டம், தோல்பாவைக் கூத்து, சிலம்பாட்டம், வளரி, புலியாட்டம், தமிழர்களின் விளையாட்டுகள். தமிழகத்தின் தாவரங்களும், விலங்குகளும் – தொல்காப்பியம் மற்றும் சங்க இலக்கியத்தில் அகம் மற்றும் புறக் கோட்பாடுகள் – தமிழாகள் போற்றிய அறக் கோட்பாடு – சங்க காலத்தில் தமிழகத்தில் எழுத்தறிவும், கல்வியும் – சங்ககால நகரங்களும் துறைமுகங்களும் – சங்க காலத்தில் ஏற்றுமதி மற்றும் இறக்குமதி – கடல் கடந்த நாடுகளில் சோழாகளின் வெற்றி.

#### அலகு 5 – இந்திய தேசிய இயக்கம் மற்றும் இந்திய பண்பாட்டிற்குத் தமிழர்களின் பங்களிப்பு 3

இந்திய விடுதலைப் போரில் தமிழா்களின் பங்கு – இந்தியாவின் பிறபகுதிகளில் தமிழ்ப் பண்பாட்டின் தாக்கம் – சுய மரியாதை இயக்கம் – இந்திய மருத்துவத்தில் சித்த மருத்துவத்தின் பங்கு – கல்வெட்டுகள், கையெ முத்துப் படிகள்– தமிழ்ப் புத்தகங்களின் அச்சு வரலாறு.

**TOTAL: 15 PERIODS**